|

◇‘높이 쌓기 경쟁’에…본딩 기술 주목

HBM 고적층 경쟁이 본격화하면서 메모리를 높게 쌓을 수 있는 패키징 기술이 중요해졌습니다. 고층 아파트를 짓는 데 한계가 있듯, HBM도 마찬가지입니다. 칩을 수직으로 많이 쌓아 올리게 되면 휨 현상이 있을 수 있고, 각 칩에서 발생한 열이 칩에 갇혀 방출이 어려워지는 등 발열 문제가 생길 수 있습니다.

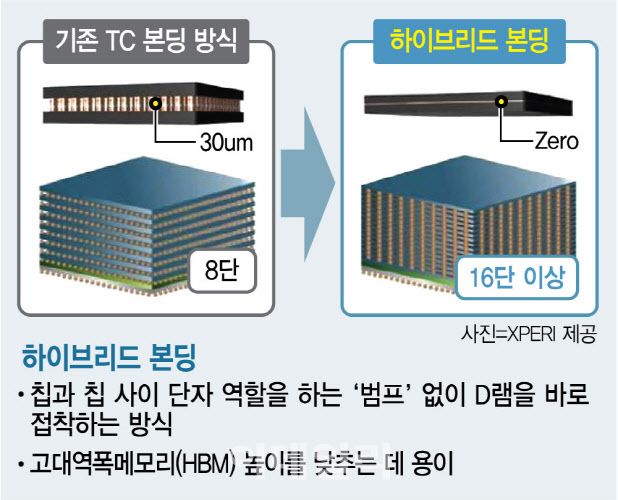

제한된 높이에서 최대한 많은 칩을 쌓아야 하는 것도 과제입니다. 현재 업계에서 정한 AI 패키징 두께 기준은 775마이크로미터(㎛)입니다. HBM은 D램 칩을 더 많이 쌓을수록 용량과 속도가 향상되는데, 최고 높이는 정해져 있으니 그 안에서 칩의 두께를 최대한 얇게 하는 기술이 필요합니다.

국내 메모리 반도체 기업들은 칩을 쌓을 때 납과 같이 전기가 통하는 돌기(범프)에 열과 압력을 가해 D램과 D램을 붙이는 열압착(TC) 방식 본딩을 사용하고 있습니다. TC 본딩은 칩과 칩을 붙일 때 가교 역할을 하는 범프가 필요하다는 한계가 있습니다.

|

◇차세대 ‘하이브리드 본딩’ 기술 개발 속도

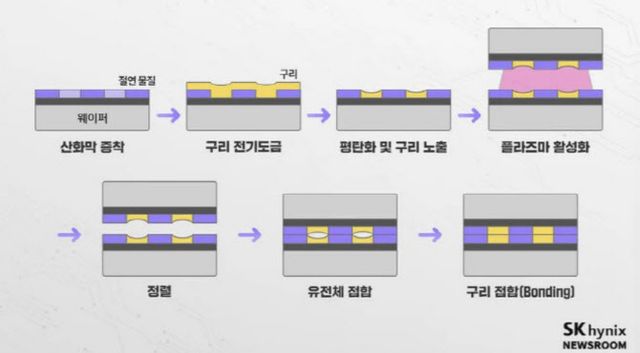

그러다가 떠오른 것이 ‘하이브리드 본딩’ 기술입니다. 하이브리드 본딩은 D램을 하나로 엮는 과정에서 TC 본딩과 다르게 칩과 칩, 또는 칩과 웨이퍼의 구리 배선을 연결하는 기술입니다. 웨이퍼에 유전체인 산화막과 금속물질 구리를 채워 넣고, 연마 작업을 통해 구리와 유전체를 평탄하게 만듭니다. 이후 플라스마 조사 공정을 거쳐 각 칩의 유전체 표면이 화학적으로 접합할 수 있도록 활성화 시킵니다.

이후 유전체는 유전체끼리, 구리는 구리끼리 붙이는 1차 접합 과정을 진행합니다. 가접합 이후 150도 정도의 열을 가해 절연체가 더 단단하게 연결되도록 합니다. 구리 부분에는 150~350도 사이의 높은 열을 가해 구리가 팽창하도록 합니다. 이렇게 되면 위와 아래 칩의 구리가 팽창하면서 사이에 있는 홈을 채우고 붙게 됩니다.

하이브리드 본딩 기술이 본격 적용되려면 1~2년의 시간이 더 걸릴 것으로 보입니다. 반도체 업계의 기술 개발로 16단 HBM 등 현재 개발되고 있는 제품에는 기존의 TC 본딩 기술로도 업계의 두께 기준을 충족할 수 있기 때문입니다. 그러나 HBM 고적층 경쟁이 피할 수 없는 흐름인 만큼, 20단 이상 제품으로 갈수록 하이브리드 본딩 기술을 어떻게 적용하는지가 핵심이 될 것으로 보입니다.

|

◇한미·한화·LG ‘3파전’…각사 전략은

기존에는 반도체 후공정 기술에서 한미반도체가 TC 본더 시장을 독점해 왔는데, 차세대 기술에 대한 중요성이 커지면서 많은 반도체 장비 기업들이 새로운 시장에 뛰어들었습니다. 최근에는 한화세미텍이 하이브리드 본딩 기술 개발에 나섰습니다.

양산 목표 시점을 보면 한화세미텍이 2026년 초 하이브리드 본더를 출시하겠다고 예고했습니다. 한미반도체는 오는 2027년 말까지 하이브리드 본더를 양산하는 것을 목표로 하고 있습니다. TC 본딩 기술 강자인 만큼, 빠른 속도로 하이브리드 본딩으로 전환할 필요가 없다는 것입니다. LG전자 생산기술원도 가장 최근 하이브리드 본더 개발 계획을 공식화했습니다. LG전자는 2028년까지 이를 양산한다는 목표를 세웠습니다.

|

하이브리드 본딩은 칩과 칩을 바로 붙이는 만큼 표면 접합면의 미세 요철을 없애고 평탄도와 청정도를 높이는 화학적기계연마(CMP) 등 기술을 확보하는 것이 중요합니다. 이에 장비 기업들은 CMP, 플라스마 등 핵심 기술을 가진 협력사들과 손을 잡고 있습니다, 특허 기술 확보를 위한 노력도 한창입니다. 한화세미텍은 하이브리드 본딩 공정에서 칩을 붙일 때 진행하는 열처리 작업인 어닐링(annealing) 작업을 두 번에 걸쳐 진행하는 것을 골자로 한 하이브리드 본더 관련 특허를 출원했습니다.

Copyright ⓒ 이데일리 무단 전재 및 재배포 금지

본 콘텐츠는 뉴스픽 파트너스에서 공유된 콘텐츠입니다.